�A���hҊǶ��ʽ�ռ�ϵ�л��֮

�����·�OӋ���M���g�v��

��Դ���A���hҊǶ��ʽ��Ӗ����

���{��о����ٝ��ARM 2410�_�l�壬�rֵ2000Ԫ��Ʒ�������e�^�ޣ��� �����v�������xȡĿǰӲ���_�l���̎����^�P�ĵğ��c���}����������x��ǡ���ĸ��ٔ���߉���������ٔ���߉�������r����ʲôӰ푡�����M��FPGAӲ��Сϵ�y�OӋ�Լ����ʹ��Cadence�M�и����·�OӋ�c����ȣ��քe���A���hҊ��λӲ���Y����Ӗ�v���������v�����λ�����~200���������dȤ���ӣ�Ո�ڱ������·��ύ�A�s��Ϣ��λ�����ޣ��ȵ��ȵá� |

|

|

|

�����·�OӋ���M���g�v�� |

|

|

200�� |

|

|

2007��07��14������1:00��5:00 |

|

|

����������W7̖�̌W��108���d |

|

|

�ı������|�T�M�룬��������ȴ�·ֱ��300���������Ľ̌W���ςȣ� |

|

|

�����A���hҊ�Ƽ��lչ����˾ |

|

|

ܛ���ИI�f��Ƕ��ʽϵ�y�֕� |

|

|

21IC��ӾW |

|

|

�����{��о�Ƽ��lչ����˾ |

|

|

�Ԓ�� 010-82600385/6 Email: consultant@farsight.com.cn |

|

|

||

| �r�g | ���}���Q | ��Ҫ���� |

|

13:00~13:30 ���� |

||

|

��Ϣ����10��� |

||

|

13:30 | 14:30 |

���}1 ���ٔ���߉�c�������_�� |

1. ���ٔ���߉��ˇ��� |

| �����}���v�ώ������ώ� �v��������10��Ƕ��ʽ���g�ĘI����6��Ƕ��ʽlinux���_�l������Ƕ��ʽLinux�Č��F�͑����������о��������_�l�^��������Ƕ��ʽ�Ŀ���漰�W�j��ͨӍ�����ƣ���Ϣ�K�˵ȸ��и��I�����纽����܉�����ɼ�ϵ�y�������ɼ�����ϵ�y��܇�dMP4�O��ȡ���ϵ�y��ֲ�к��Ľ���X86/ARM/XSCALE/PowerPC/MIPS�ȸ��N�wϵ�Y��ƽ�_����ֲLinux�Ⱥˣ�����Ƕ��ʽLinux�Č��r�Ժ�CELinux�����c�������о��� | ||

|

��Ϣ����10��� |

||

|

14:40 | 15:40 |

���}2 FPGAӲ��Сϵ�y�OӋ |

1��FPGAСϵ�y�����Լ�Ӳ��ϵ�y�Ę��� |

|

��Ϣ����10��� |

||

| �����}���v�ώ���Ҧ�ώ� �������պ����W�Ԅӻ����I��ʿ�Wλ��FPGA��Ӗ�v������8���FPGA��DSPϵ�yӲ���_�l���ɹ��_�l���l���d�����وD�sϵ�y���t��D��ɼ����s�͂�ݔϵ�y������MPEG4/H.264�ľW�j�O��ϵ�y������(1GHz)����(4�w)DSP�D��̎��ϵ�y, ����Ҏģ����500�f�TFPGA��Cƽ�_(Altera StratixII EP2S180)��Ŀǰ���څ��c��ؓ؟��헡�ʮ�塱�͡�ʮһ�塱�A���Ŀ�Լ�863���c�Ŀ��Ӳ��ܛ���OӋ�ȹ�������4���һֱ����ҕ�l�͈D��̎���I��ĸ���DSPϵ�yӲ��ܛ����FPGAϵ�y���OӋ���_�l�����зdz��S���ĸ���ϵ�y�OӋ����ͨTI��˾��C6000ϵ�и���DSP��Altera��˾��ȫϵ��FPGA/CPLD�� | ||

|

15:50 | 16:50 |

���}3 Cadence�����·�OӋ�c���� |

���Ƚ�B�ڸ����·�OӋ����������̖�����ԡ��r��ƥ���Լ�늴ż����Ե�һϵ�І��}��Ȼ���v�������Cadence��SPB��Silicon-Package-Board��ܛ�����߽�Q�������}����Ҫ��������̖���䡢���_��ͬ�r�_�P���ȵķ����c������ͬ���r���·�ĕr��ƥ�䷽�����ؓ�Y������s���Ĵ_�������ڼs���IJ��ֲ�������������������ٲ����̖�ķ��漰�����ȃ��ݡ� |

| �����}���v�ώ������ώ� �L�ڏ��½̌W�c���й�������Ҫ�о���������W�jͨ�š�ҕ�l/�D��̎����������ȡ������c��ؓ؟�^�����塱�͡����塱�A���Ŀ�Լ�863���c�Ŀ��Ӳ��ܛ���OӋ�ȹ���������15���Ӳ���OӋ�������ǽ�6���һֱ�������P�I��ĸ���DSPϵ�yӲ��ܛ����FPGA�_�l�����·�OӋ���������зdz��S���ĸ���PCB�OӋ����ͨTI��˾��C6000��ADI��˾��TigerSHarc-201��ϵ�и���DSP���ɹ��_�l�˶�������DSP��FPGA�Y�ϵĸ��y���Ŀ���������L��̎����ϵ�y���_�l����Ϥ��N�D��/ҕ�l���s�㷨����Ӌ��C�W��ȿ����ϰl��Փ��20��ƪ�� | ||

|

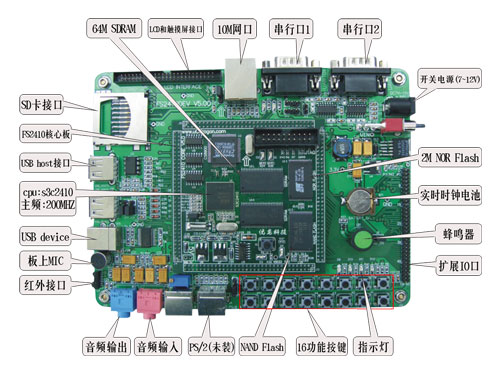

16:50~17:10 �F���骄��ӣ�ARM9 2410�_�l�壬�����������D��ʾ��  |

||

|

|

|