Ƕ��ʽӲ���·�OӋ

�r�g��2018-03-22���ߣ��A���hҊ

һ��Ƕ��ʽӲ���·�OӋ����

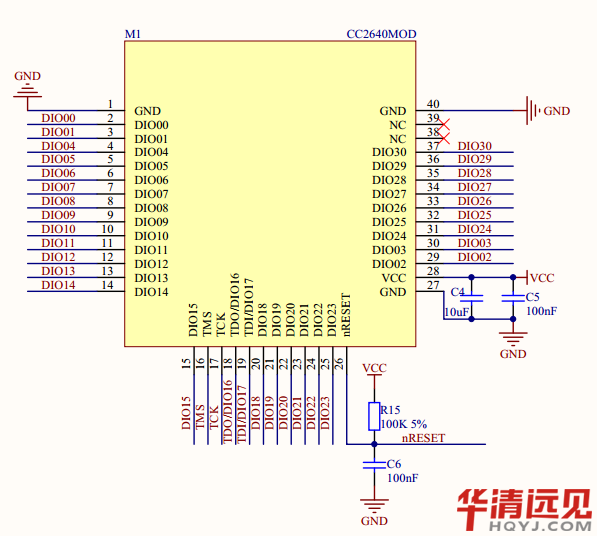

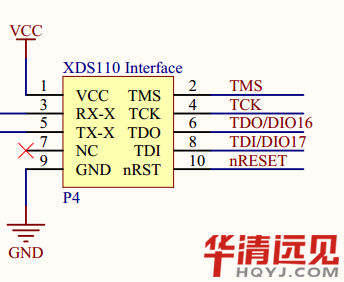

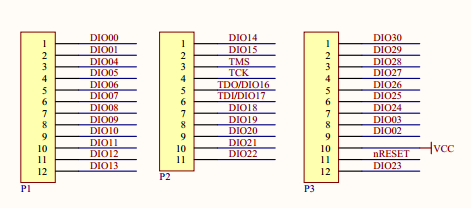

�S�����W���˹����ܼ��g�İlչ���҂�������Խ��Խ���ܻ�����Ϣ���������֙C�������֭h�������i�����ܱ��䣬�Ԅ��{�C���˵����ܮaƷ�ӳ����F��������M�����ܕr�����҂��ĮaƷ���O��Ҫ���F���ܻ��������õ�������ļ��g��Ƕ��ʽ���g�� Ƕ��ʽ���g��ܛ����Ӳ����Y��һ�T�W�ƣ�����Ƕ��ʽܛ����Ƕ��ʽӲ����Ƕ��ʽܛ����Ӳ���������ܮaƷ����ĵIJ��֣�Ƕ��ʽӲ���ஔ�ڮaƷ���|����������Ƕ��ʽܛ������������Ƕ��ʽܛ���Ŀ�������ɮaƷ�����Ĺ��ܣ���Ƕ��ʽܛ�����d�w��Ƕ��ʽܛ���ஔ�ڮaƷ�Ĵ��X���ǮaƷ���`�꣬�]����Ƕ��ʽܛ����Ӳ������һ�яU�~���F���o��������ͬ�ӣ��]����Ƕ��ʽӲ����Ƕ��ʽܛ�����o�������������fǶ��ʽӲ����ܛ��ͬ����Ҫ���������o��ɣ�ȱһ���ɡ� �S�������·�İlչ��Ƕ��ʽӲ���Ĺ����OӋ�������f���^���Σ��������r��ֻ��Ҫ����оƬ�S���ṩ�ą����·�OӋ���ɣ�Ƕ��ʽӲ���OӋ�ĺ���Խ��Խƫ��ɿ����OӋ��늴�ݗ�䣬늴ż����OӋ���������Ҍ����OӋ�{��ģ�K�_�l����·�D�������v��Ƕ��ʽӲ���·�OӋ�е�ע����헡� �����{�����g���{��оƬCC2640 “�{��”���g����һ�N�̾��x���ͳɱ������ĵğo���B�Ӽ��g����һ�N�܉F�Z���͔����o����ݔ���_���Է���������2.4GHz��ISM (�����I���ƌW���t�W)�l�Σ����ݔ������ߞ�ÿ��1Mb/s���ԕr�ַ�ʽ�M��ȫ�p��ͨ�ţ��{���հl����һ����Чͨ�ŷ�����10�ף����ù��ʷŴ�������ʹͨ�ž��x�_��100�����ҡ�����������{���Mؓ؟�����f���OӋ�{��������뷨��“�Y�����|ج��”�� CC2640 ������һ��o�������� (MCU)����Ҫ�m���� Bluetooth®���� ���á����������� SimpleLink™ CC26xx ϵ���еĽ�����Ч�ͳ����� 2.4GHz RF �����������ИO�͵���Դ RF �� MCU ����Լ�����ģʽ���ģ��ɴ_��Խ��늳�ʹ�É������m��С�ͼ~��늳ع���Լ�����Դ�ɼ��͑�����ʹ��. CC2640 ����һ��Cortex-M3�Ⱥˣ��������l48MHZ,128K Flash,28K SRAM ,4�����r����15��GPIO,���ڣ�I2C��12λADC�ȳ������Oһ����ȫ��Ӳ���YԴ�dz��S������ȫ�M���ճ��o�����á� �����{��оƬCC2640Ӳ���·�OӋע����� �OӋ��MCU����ĵ�Ƕ��ʽϵ�yӲ���·��Ҫ������������M�оC�Ͽ��]����Ҫ���]�Ć��}�^�࣬�@��o���ׂ��eҪע��Ć��}. 1. MCU�x�� �x�� MCU �rҪ���] MCU ���܉���ɵĹ��ܡ�MCU �ăr���ġ����늉���I/O ���ƽ�����_��Ŀ�Լ� MCU �ķ��b�����ء�MCU �Ĺ��Ŀ��ԏ���늚����܅����в鵽�����늉��� 5V��3.3V �Լ� 1.8V ����늉����ģʽ�������ܺ������� MCU ��I/O�YԴ���� MCU �x�͕r���L��һ�����_����������Ժ���OӋʹ�á��҂��@���x���ʹ��CC2640 CPU�ğo���{��ģ�K���� CC2640 �{���o��ģ�K�·ԭ��D���£�   XDS110�{ԇ�ӿ� 2. �Դ�·�OӋ

��1�����]ϵ�y���Դ����������ϵ�y��Ҫ�N�Դ����24V��12V��5V����3.3V�ȣ���Ӌ����Ҫ���ٹ��ʻ���������mA������Ӌ���Դ�����ʕrҪ���]һ�����������ɰ���ʽ“�Դ������=2×����������”��Ӌ�㡣

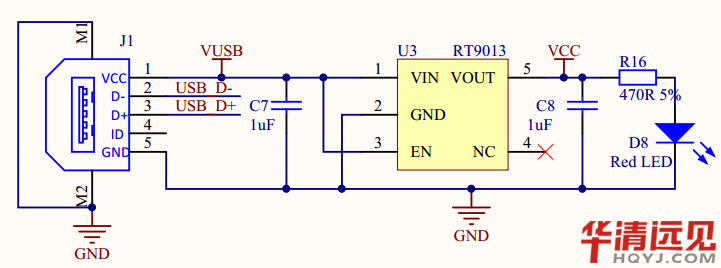

��2�����]оƬ�c�������Դ�����Ե�����һ�����S�Դ���ӷ����� ±5% �ԃȡ�����A/D�D�QоƬ�ą���늉�һ��Ҫ�� ±1% �ԃȡ� ��3�����]�����Դ��ʹ���Դģ�K߀��ʹ������Դ�� ���@���҂�ʹ�õ͉�������������پ��Է�����RT9013�o�{���o��ģ�K���. CC2640�İl���������10 mA���ң�RT9013ݔ����������_�� 500mA, ��ȫ�M��CC2640�������Դ��Ҫ�� �Դ�·�OӋ���£�

3. ��ͨIO���·�OӋ

��1��������������裺���]�ÃȲ������ⲿ��/������裬�Ȳ���/������ֵһ���� 700Ω ���ң�����ģʽ����ʹ�á��ⲿ��/������������Ҫ���x 10KΩ��1MΩ ֮�g�� ��2���_�P��ݔ�룺һ��Ҫ���C�ߵ�늉�������������r�¸��ƽ�����Դ늉������ƽ���ǵص��ƽ������ⲿ�·�o�����_�^�ָߵ��ƽ�����ߵ������^��ɿ��]�� A/D �ɼ��ķ�ʽ�OӋ̎�������։���ʽ�еIJɘ��c��Ҫ���]�։������x��ʹԓ�cͨ�^�ɘӶ˿ڵ������С�ڲɘ���Сݔ���������t�o���M�вɘӡ� ��3���_�P��ݔ��������ԭ�t�DZ��Cݔ�����ƽ�ӽ��Դ늉������ƽ�ӽ����ƽ��I/O �ڵ����{���һ����ڷų��������С����Ԫ������������Dz��õ��ƽ���Ƶķ�ʽ��һ����r�£���ؓ�dҪ��С��10mA���t����оƬ���_ֱ�ӿ��ƣ������ 10~100mA �r�������O�ܿ��ƣ��� 100mA��1A �r�� IC ���ƣ����������t�m�����^������ƣ�ͬ�r���hʹ�ù�늸��xоƬ�� �@���҂����_�l��ĵ�I/O��ȫ���������������Ñ��M�ж����_�l�͜yԇ��C�����D��ʾ��

4. A/D�·�cD/A�·

��1��A/D�·��Ҫ���ǰ�˲ɘӻ���ԭ����������͡�����ͺ�늉��͂��������ò�ͬ�IJɼ��·������ɼ�����̖����߀Ҫ���]����M����̖�Ŵ� ��2��D/A�·�����] MCU �����_ͨ�^�ηNݔ���·���ƌ��H���� 5.�����· ��������·Ҫע���OӋ�������c���y��Ҫ�к��m����̖���x��ʩ�ȡ����u���OӋ�IJ���r��һ��Ҫ�ژ�����ݔ��ݔ���������z�y�ף��Է����Ų��e�`�r�y���� 6.���]���� �����OӋ�����H�H�Ǟ���ʡ늣�����ĺ�̎���ڽ������Դģ�K��ɢ��ϵ�y�ijɱ�����������ĜpСҲ�p����늴�ݗ��͟����ĸɔ_���S���O��ضȵĽ��ͣ����������t�������L��Ҫ��������һ����Ҫע�������c�� ��1�����������еĿ�����̖��Ҫ���������������Ҳ�й��Ć��}��Ҫ���]�������������һ���μ���ݔ����̖�����Ҳ�͎�ʮ�����¡�����һ�������˵���̖����������_��������������Ҫ���]��������茦ϵ�y�����ĵ�Ӱ푡� ��2�����õ�I/O�ڲ�Ҫ�ҿգ�����ҿյ�Ԓ��������һ�c�c�ɔ_�Ϳ��ܳɞ鷴����ʎ��ݔ����̖����MOS�����Ĺ��Ļ���ȡ�Q���T�·�ķ��D�Δ��� ��3����һЩ���СоƬ�Ĺ���Ҳ��Ҫ���]�����ڃȲ���̫���s��оƬ�����Ǻ��y�_���ģ�����Ҫ�����_�ϵ�����_���������е�оƬ���_�ڛ]��ؓ�d�r����늴�Ų���1��������ؓ�d�����Ժ��ܹ��ĺܴ� 7.���]�ͳɱ� ��1�����_�x�����ֵ�c���ֵ������һ��������裬����ʹ��4.5K-5.3K����裬���X�þ��x������5K�������Ј��ϲ�����5K����ֵ����ӽ�����4.99K������1%���������5.1K������5%������ɱ��քe�Ⱦ��Ȟ�20%��4.7K��4����2����20%���ȵ������ֵֻ��1��1.5��2.2��3.3��4.7��6.8�ׂ�e����10��������������Ƶأ�20%���ȵ����Ҳֻ�����ώNֵ������x��������ֵ�ͱ��ʹ�ø��ߵľ��ȣ��ɱ��ͷ��ˎױ����s�������κκ�̎�� ��2����Ҫʲô���x��õġ���һ������ϵ�y�в�����ÿһ���ֶ������ڸ��٠�B���������ٶ�ÿ���һ���ȼ����r����Ҫ����������߀�o��̖�����Ԇ��}����O���ؓ��Ӱ�. ����Ƕ��ʽ���̎�����Ҫ����Ƕ��ʽܛ���OӋ��ҲҪ����Ӳ���OӋ�������ܿ���Ӳ��ԭ��D���܉�����Ӳ���Ĺ���ԭ�����@���҂����ܸ��õľ�����Ч��Ƕ��ʽܛ�������{ԇ�aƷ����Q�O����ϕr�����܉��ܛ��Ӳ���ĽǶȁ��������}�ͽ�Q���}�� ���Ͼ������@��Ҫ�ʹ�ҷ������P��Ƕ��ʽӲ���OӋ��ע����헣�ϣ����ͬ�W������������ ���P�YӍ

�l���uՓ

|

ȫ����ԃ�Ԓ��400-611-6270���p���ռ�������Ո���ֵ���֙C��15010390966

�ھ���ԃ�� ���ώ�QQ��3337544669���� ���ώ�QQ��1462495461���� ���ώ� QQ��3108687497��

��I��ӖǢՄ������010-82600901��ԺУ����ǢՄ������010-82600350���ھ���ԃ��QQ��248856300��

Copyright 2004-2018 �A���hҊ�����Ƽ����F ������� ����ICP��16055225̖���������W����11010802025203̖