DS1302�r犱���оƬ����ܿ��x����

�r�g��2018-04-23 ��Դ��δ֪

DS1302�r犱���оƬ����ܿ��x����

�r�g��2018-04-23 ��Դ��δ֪

������

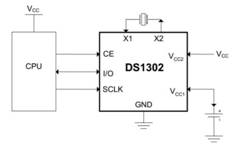

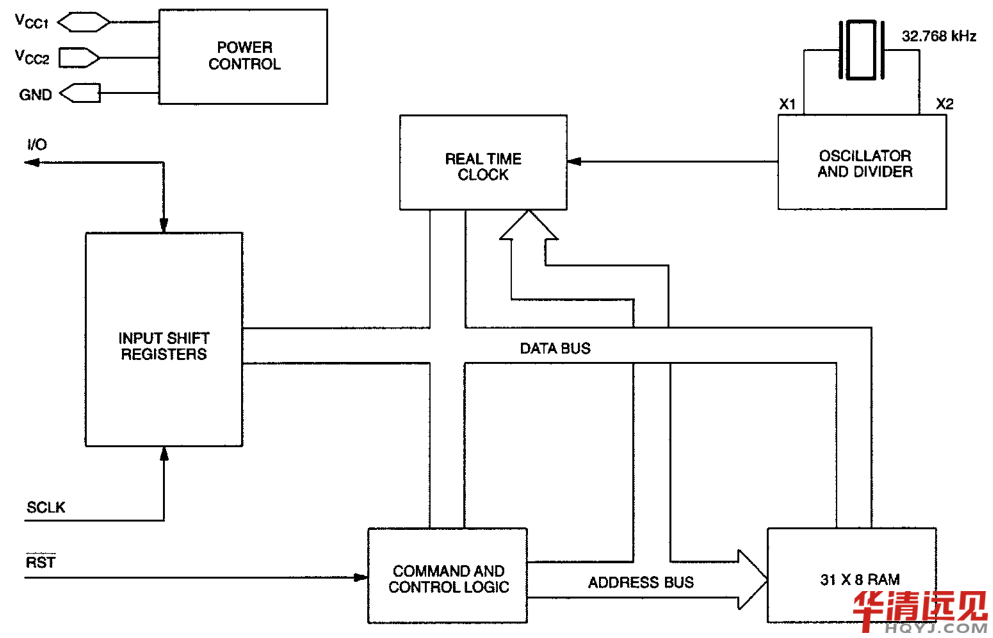

DS1302��DALLAS��˾�����������늕r�оƬ��оƬ�Ќ��r�r��՚v���ܣ���31*8bits�o�BRAM������ͨ�^���нӿڷ�ʽ��̎����(stm32��ARM��)�M��ͨ�Ł��x��RAM���ЃɷN���ͷ�ʽ�����ֹ����ͺͶ��ֹ����͡��Ȳ����r�r��՚v����߉�·�����ṩ�r���֡��롢�ꡢ�¡�����Ϣ(2100��֮ǰ������)�������Ԅ��{���c�꣬�c���}����24С�r��12С�r�ɷN��ʽ��ʾ��DS1302��̎����֮�gͨ�^�������B�ӣ�1��CE(���ƽ��Ч)ʹ�ܾ�;2��I/O(Data line)������;3��SCLK(serial clock)���Еr犾���DS1302���е��ģ��ӿں���(��̎����֮�gֻ��Ҫ�������_)�����ȸߣ����ɔ_���ȃ��c������늉�(2.0V~5.5V)�cTTL���ݡ�DS1302����ݼĴ��������ƼĴ�������늼Ĵ������r�ͻ�l�Ĵ�����RAMͻ�l�Ĵ�����RAM�惦��(31*8bits)��

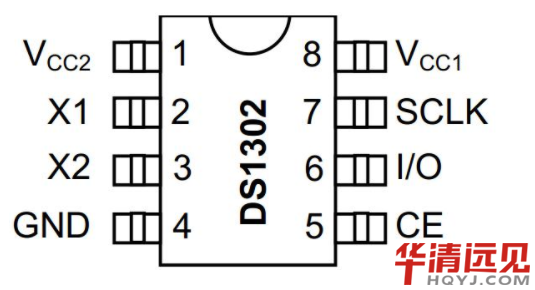

DS1302���_�������

���_����

X1 X2 ��32.768KHz�������_

GND �ӵؾ�

CE ʹ�����_

I/O �����հl���_

SCLK �r����_

Vcc1,Vcc2 ������_

DS1302��D���£�

������:

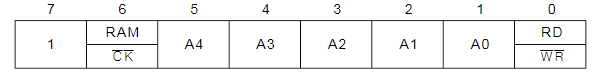

������ռ8������λ�����D��

�����ֹ��Á���ʼ��ÿ�Δ����Ă�ݔ�������ֹ������λ(bit 7)����O�Þ�1������O�Þ�0�����������ֹ��Bit6 ��0�r��ָ�����r�g\���ڔ����x���������1�r��ָ����RAM�����M���x����bit1 �� bit5ָ����Ҫ���x���ļĴ������ǂ�(оƬ�Ȳ��Ĵ�����ַ)�����һ��bitλ(bit0)�����0�r��ʾ����(input)�������1�r��ʾ�x��(output)���������ڂ�ݔ�ĕr�����Ȃ�ݔ�ͱ���λ(bit0)��

ʹ���Լ��r犿��ƣ�

��Ҫ��ݔ�����r��Ҫ�O��ʹ�����_(CE)����ƽ��

ʹ�����_(CE)�ĸߵ��ƽ�Á��ṩ�ɷN���ܡ���һ�N���O�Þ���ƽʹ��оƬ���˕r���S�����ֹ�\��ַ����ȥ�L��DS1302�Ȳ�����λ�Ĵ������ڶ��N��CE��̖�ṩһ�����ڽKֹ������ݔ(�oՓ�dž��ֹ���ݔ߀�Ƕ��ֹ���ݔ)�Ĺ��ܡ�

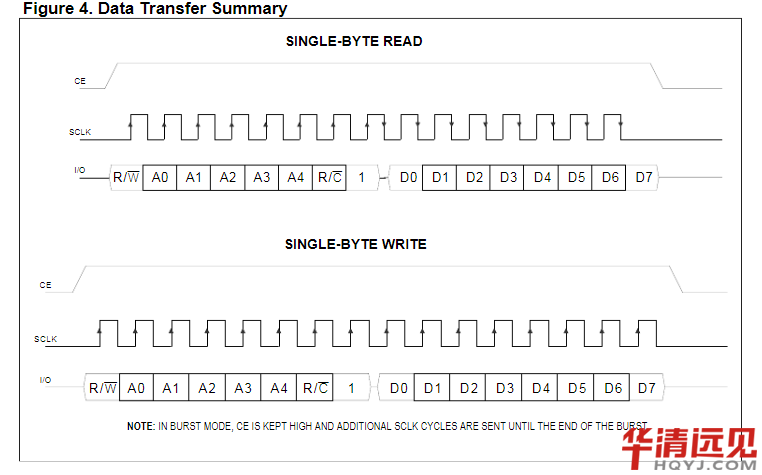

SCLK�r犾��ϵ�һ�������غͺ���o����һ���½��ؽM�ɵ�һ������������һ���r����ڡ�̎������DS1302���딵���r��DS1302���ڕr����ڵ������ؕr�ɼ�I/O(������)�ƽ��B��̎������DS1302�xȡ�����r��DS1302���ڕr����ڵ��½��ؕr�O��I/O(������)�ƽ��B�����CE(ʹ����̖��)ݔ�����ƽ�����еĔ�����ݔ�����Kֹ����I/O(������)����׃�ɸ���B���Dչʾ�ˆ��ֹ����x���r��D���ڄ���늕r��CE(ʹ����̖��)���̎�ڵ��ƽ��B(����2.0V)��߀�о�����CE(ʹ����̖��)�ĵ��ƽ׃����ƽ���gSCLK(���Еr���̖��)��횱��ֵ��ƽ��

ݔ�딵�� (write)

���Ȃ�ݔһ������������(bit0 ����ƽ)ռ��ǰ8���r����ڣ��ھo�S�����B�m8���r����ڂ�ݔһ��8����λ(һ���ֹ�)�Ĕ�����ÿһ������λ������SCLK(���Еr犾�)�������ؕr�O��I/O(������)����������l�����~��ĕr����ڣ��@Щ�~��ĕr����ڌ��������ԡ������Ă�ݔ���Ȃ���ÿ���ֹ��ĵ�bitλ��

ݔ������(read)

���Ȃ�ݔһ���x��������(bit0 ����ƽ)ռ��ǰ8���r����ڣ��ھo�S�����B�m8���r����ڂ�ݔһ��8����λ(һ���ֹ�)�Ĕ�������Ҫע����ǣ������ĵ�һ������λ(D0)ݔ�����������ֵ�bit7�������ڵ��½���ݔ����������l�����~��ĕr����ڣ��@Щ�~��ĕr����ڌ��������ԣ��˕rCE(ʹ����̖��)߀�Ǹ��ƽ��ͬ�r��I/O���_��ÿ���r����������ؕr�����B�������Ă�ݔ���Ȃ���ÿ���ֹ��ĵ�bitλ��

ͻ�lģʽ��

�����Ǖr�/�՚v�Ĵ���߀��RAM�Ĵ���������ʹ��ͻ�lģʽ�M���L������Ҫ�������ֵĵ�ַλ(bit1 ~ bit5 )ȫ���O�Þ�1���O�������ֵ�bit6(ָ���������Ǖr�/�՚v�Ĵ���߀��RAM�Ĵ���)���O�������ֵ�bit0(����ָ�����x߀�nj�)���L���r�/�՚v�Ĵ����ĕr���ڵ�ַ9~31��λ���Ǜ]�д惦���|�ġ�߀�����L��RAM�Ĵ����ĕr���ڵ�ַ31��λ�Û]�д惦���|����ͻ�lģʽ�oՓ���x߀�nj����Ǐ�0��ַ��bit0λ�_ʼ�ġ�

����ͻ�lģʽ���r�\�՚v�Ĵ����r��ǰ8���Ĵ�����횰�������딵�������ǣ���ͻ�lģʽ��RAM�Ĵ����r���͛]��Ҫ�����е�31�ֹ��ļĴ���ȫ�����딵������ݔ��ÿһ���ֹ����������뵽RAM�Ĵ����У������Ƿ��ݔ��31���ֹ���

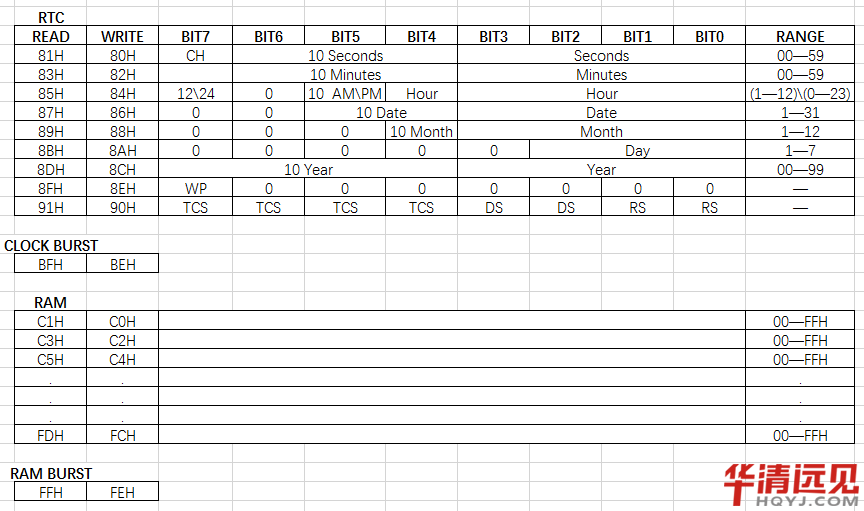

�r�/�՚v

�x�����ļĴ������ԫ@ȡ�r�g�����ڡ�����3 �f���˕r�g\���ڼĴ�������푑��ļĴ��������Á��O�Õr�g�����ڡ���BCD�a�ĸ�ʽ�ѕr�g/���ڔ���������푑��ļĴ����С�

����ҹ�賿�ĕr����f����ʾ���ڎļĴ������Ñ������Զ��x��ʾ������Ĕ�ֵ�Ƕ��٣����ǔ�ֵ������B�m��(���磺1��ʾ�����죬��ô2�ͱ�ʾ����һ��3�ͱ�ʾ���ڶ��ȵ�)�����ݔ����һЩ������߉�ĕr�g�������ڣ�������һЩδ���x�ĽY����

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers the rising edge of CE.

The countdown chain is reset whenever the seconds register is written. Write transfers occur on the falling edge of CE. To avoid rollover issues, once the countdown chain is reset, the remaining time and date registers must be written within 1 second.

DS1302�����\����12С�r�ƺ�24С�r�ƃɷNģʽ��С�r�Ĵ�����bit7λ���ڛQ���\����12С�r��߀��24С�r��ģʽ���O�Þ�1(���ƽ)�r����12С�r��ģʽ�����\����12С�r��ģʽ�r��bit5�Á���ʾ������߀������(AM/PM),��1(���ƽ)�r��ʾPM�����\����24С�rģʽ�r��bit5�Á���ʾ��2��10С�r(20-23С�r)�����ГQģʽ�ĕr��(��bit7)��Ҫ���³�ʼ��С�r�Ĵ�����

�r�ֹͣ��־��

��Ĵ�����bit7λ�Ǖr犽Kֹ��־λ����bit7�O�Þ�1�r���r���ʎ������ֹͣ��ʎ�˕rDS1302�M����ĵĴ��Cģʽ���������С��100nA����bit7�O�Þ�0�r���r犌��_ʼ�������O�䄂��늕rԓλ�]�ж��x��

�����o�

���ƼĴ�����bit7�nj����oλ(WP)��ǰ7��bitλ(bit0 ~ bit6)���O��λ0������x���ƼĴ�����ǰ7��bitλ(bit0 ~ bit6)���x�������h��0���ڌ��r�/�՚v����RAM�Ĵ���֮ǰ�����ƼĴ�����bit7�����0���������oλ(WP)��1�r������ֹ���κ������Ĵ����Č���������ˣ���������O��Ĵ��Ќ������ͱ���Ȍ������oλ(WP)��0���O�䄂��늕rԓλ�]�ж��x��

�����늼Ĵ�����

ԓ�Ĵ����Q����DS1302�ij�����ԡ�

�r�/�՚vͻ�lģʽ��

�ɕr�/�՚v�����ց�ָ��ͻ�lģʽ���������@�Nģʽ�£�8���r�/�՚v�Ĵ������Ա��B�m���x�����ߌ��롣�x�����ߌ�����䌍λ����0��ַ�ĵ�0��bitλ��

����O�Ì����oλ��1�r���ڕr�/�՚vͻ�lģʽ����8���r�/�՚v�Ĵ����]��һ�����l��׃��(�������ƼĴ���)������������ͻ�lģʽ�²����L����

���_ʼ�x�r犵ĕr��ǰ�ĕr�g���D�Ƶ�һ�����üĴ����С��r�g��Ϣ���Ă��üĴ������x���������@���^���Еr犿��ܰl��׃�����@���������ڕr犼Ĵ������r��Ҫ�����xȡ�r犼Ĵ�������r��

RAM��

�o�BRAM��С�� 31*8bits����RAM��ַ���g�������ĵ�ַ���B�m�ġ�

RAMͻ�lģʽ��

��RAM�����ց�ָ��ͻ�lģʽ���������@�Nģʽ�£�31��RAM�Ĵ������Ա�ϵ���x�����ߌ��롣�x�����ߌ�����䌍λ����0��ַ�ĵ�0��bitλ��

�Ĵ����śr��

��3չʾ�˼Ĵ���������ʽ�ĸśr��

�����x��

��DS1302��X1��X2���_�Ͽ���朽�һ��32,768kHz�ľ���

��3���£�

��4 ���£�