һ��Ƕ��ʽӲ���·�O(sh��)Ӌ(j��)����

�S����(li��n)�W(w��ng)���˹����ܼ��g(sh��)�İl(f��)չ���҂�������Խ��(l��i)Խ���ܻ�����Ϣ���������֙C(j��)�������֭h(hu��n)�������i�����ܱ��䣬�Ԅ�(d��ng)�{�C(j��)���˵����ܮa(ch��n)Ʒ�ӳ����F��������M(j��n)�����ܕr(sh��)�����҂��Įa(ch��n)Ʒ���O(sh��)��Ҫ��(sh��)�F(xi��n)���ܻ��������õ�������ļ��g(sh��)��Ƕ��ʽ���g(sh��)��

Ƕ��ʽ���g(sh��)��ܛ����Ӳ����Y(ji��)��һ�T�W(xu��)�ƣ�����Ƕ��ʽܛ����Ƕ��ʽӲ����Ƕ��ʽܛ����Ӳ����(g��u)�����ܮa(ch��n)Ʒ����ĵIJ��֣�Ƕ��ʽӲ���ஔ(d��ng)�ڮa(ch��n)Ʒ���|����������Ƕ��ʽܛ������������Ƕ��ʽܛ���Ŀ�������ɮa(ch��n)Ʒ����(y��ng)�Ĺ��ܣ���Ƕ��ʽܛ�����d�w��Ƕ��ʽܛ���ஔ(d��ng)�ڮa(ch��n)Ʒ�Ĵ��X���Ǯa(ch��n)Ʒ���`�꣬�]����Ƕ��ʽܛ����Ӳ������һ�яU�~���F���o(w��)��������ͬ�ӣ��]����Ƕ��ʽӲ����Ƕ��ʽܛ�����o(w��)�������������fǶ��ʽӲ����ܛ��ͬ����Ҫ���������o��ɣ�ȱһ���ɡ�

�S�������·�İl(f��)չ��Ƕ��ʽӲ���Ĺ����O(sh��)Ӌ(j��)����(du��)��(l��i)�f���^��(ji��n)�Σ������(sh��)��r��ֻ��Ҫ����(j��)оƬ�S���ṩ�ą����·�O(sh��)Ӌ(j��)���ɣ�Ƕ��ʽӲ���O(sh��)Ӌ(j��)�ĺ���Խ��(l��i)Խƫ��ɿ����O(sh��)Ӌ(j��)��늴�ݗ�䣬늴ż����O(sh��)Ӌ(j��)������(l��i)���Ҍ����O(sh��)Ӌ(j��)�{(l��n)��ģ�K�_�l(f��)����·�D������(l��i)�v��Ƕ��ʽӲ���·�O(sh��)Ӌ(j��)�е�ע�����(xi��ng)��

�����{(l��n)�����g(sh��)���{(l��n)��оƬCC2640

“�{(l��n)��”���g(sh��)����һ�N�̾��x���ͳɱ������ĵğo(w��)���B�Ӽ��g(sh��)����һ�N�܉�?q��)��F(xi��n)�Z(y��)���͔�(sh��)��(j��)�o(w��)����ݔ?sh��)��_���Է���������2.4GHz��ISM (�����I(y��)���ƌW(xu��)���t(y��)�W(xu��))�l�Σ����ݔ������ߞ�ÿ��1Mb/s���ԕr(sh��)�ַ�ʽ�M(j��n)��ȫ�p��ͨ�ţ��{(l��n)���հl(f��)����һ����Чͨ�ŷ�����10�ף����ù��ʷŴ�������ʹͨ�ž��x�_(d��)��100�����ҡ�����������{(l��n)���Mؓ(f��)؟(z��)�����f���O(sh��)Ӌ(j��)�{(l��n)��������뷨��“�Y(ji��)�����|ج��(m��ng)”��

CC2640 ������һ��o(w��)�������� (MCU)����Ҫ�m���� Bluetooth

®���� ��(y��ng)�á����������� SimpleLink™ CC26xx ϵ���еĽ�(j��ng)��(j��)��Ч�ͳ����� 2.4GHz RF �����������ИO�͵���Դ RF �� MCU ����Լ�����ģʽ���ģ��ɴ_��Խ��늳�ʹ�É������m��С�ͼ~��늳ع���Լ�����Դ�ɼ��͑�(y��ng)����ʹ��.

CC2640 ����һ��(g��)Cortex-M3��(n��i)�ˣ��������l48MHZ,128K Flash,28K SRAM ,4��(g��)���r(sh��)����15��(g��)GPIO,���ڣ�I2C��12λADC�ȳ������O(sh��)һ��(y��ng)��ȫ��Ӳ���YԴ�dz��S������ȫ�M���ճ��o(w��)����(y��ng)�á�

�����{(l��n)��оƬCC2640Ӳ���·�O(sh��)Ӌ(j��)ע�����(xi��ng)

�O(sh��)Ӌ(j��)��MCU����ĵ�Ƕ��ʽϵ�y(t��ng)Ӳ���·��Ҫ����(j��)��������M(j��n)�оC�Ͽ��]����Ҫ���]�Ć��}�^�࣬�@��o���ׂ�(g��)�eҪע��Ć��}.

1. MCU�x��

�x�� MCU �r(sh��)Ҫ���] MCU ���܉���ɵĹ��ܡ�MCU �ăr(ji��)���ġ����늉���I/O ���ƽ�����_��(sh��)Ŀ�Լ� MCU �ķ��b�����ء�MCU �Ĺ��Ŀ��ԏ���늚����܅���(sh��)�в鵽�����늉��� 5V��3.3V �Լ� 1.8V ����늉����ģʽ�������ܺ������� MCU ��I/O�YԴ���� MCU �x�͕r(sh��)���L��һ�����_����������Ժ���O(sh��)Ӌ(j��)ʹ�á��҂��@���x���ʹ��CC2640 CPU�ğo(w��)���{(l��n)��ģ�K����

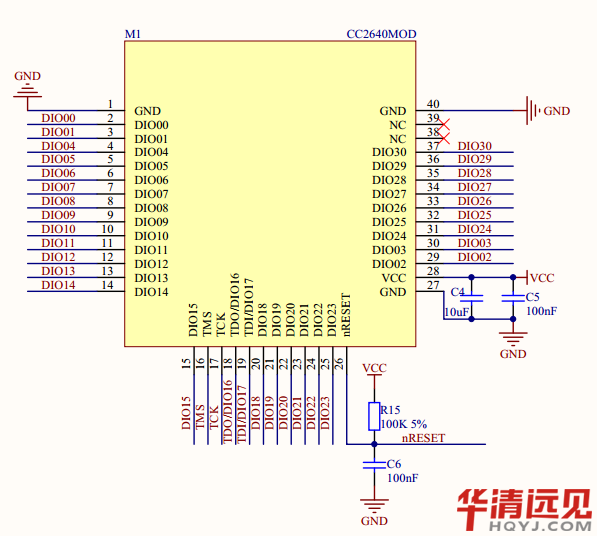

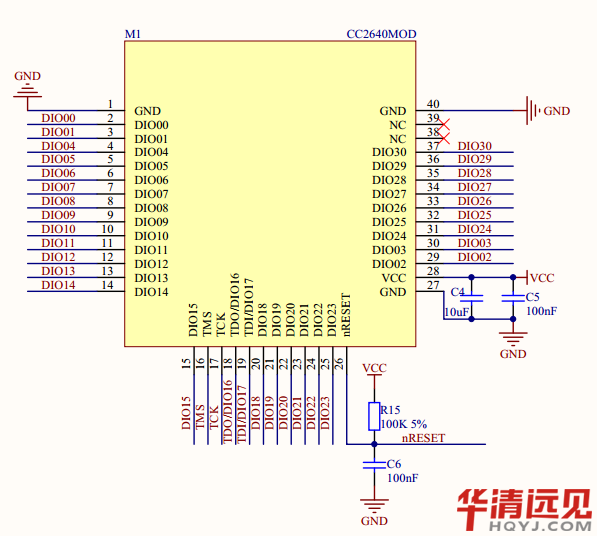

CC2640 �{(l��n)���o(w��)��ģ�K�·ԭ��D���£�

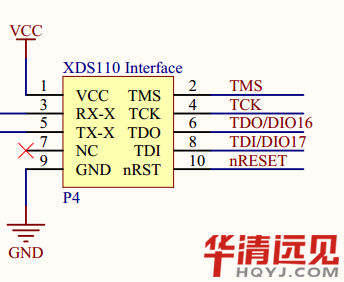

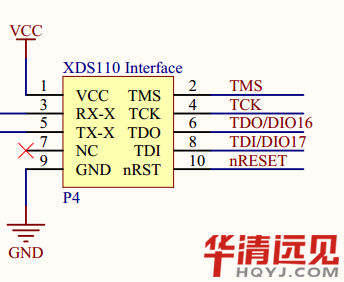

XDS110�{(di��o)ԇ�ӿ�

2. �Դ�·�O(sh��)Ӌ(j��)

��1�����]ϵ�y(t��ng)��(du��)�Դ����������ϵ�y(t��ng)��Ҫ�N�Դ����24V��12V��5V����3.3V�ȣ���Ӌ(j��)����Ҫ���ٹ��ʻ���������mA������Ӌ(j��)���Դ�����ʕr(sh��)Ҫ���]һ�����������ɰ���ʽ“�Դ������=2×����������”��(l��i)Ӌ(j��)�㡣

��2�����]оƬ�c������(du��)�Դ����(d��ng)�Ե�����һ�����S�Դ����(d��ng)������ ±5% �ԃ�(n��i)����(du��)��A/D�D(zhu��n)�QоƬ�ą���늉�һ��Ҫ�� ±1% �ԃ�(n��i)��

��3�����]�����Դ��ʹ���Դģ�K߀��ʹ������Դ��

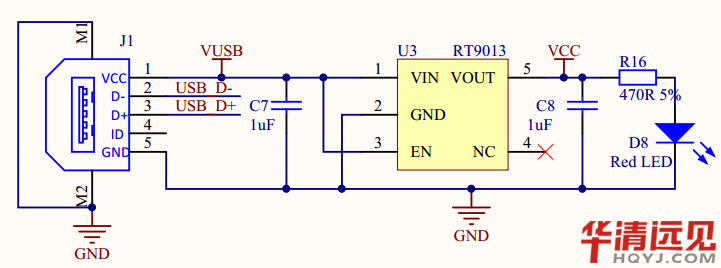

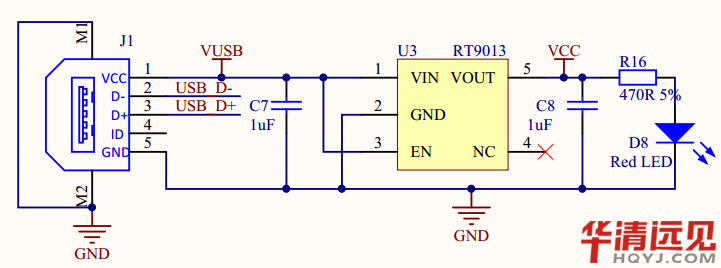

���@���҂�ʹ�õ͉�������������پ��Է�(w��n)����RT9013�o�{(l��n)���o(w��)��ģ�K���.

CC2640�İl(f��)���������10 mA���ң�RT9013ݔ����������_(d��)�� 500mA, ��ȫ�M��CC2640��(du��)�����Դ��Ҫ�� �Դ�·�O(sh��)Ӌ(j��)���£�

3. ��ͨIO���·�O(sh��)Ӌ(j��)

��1��������������裺���]�Ã�(n��i)�������ⲿ��/������裬��(n��i)����/������ֵһ���� 700Ω ���ң�����ģʽ����ʹ�á��ⲿ��/����������(j��)��Ҫ���x 10KΩ��1MΩ ֮�g��

��2���_�P(gu��n)��ݔ�룺һ��Ҫ���C�ߵ�늉�������������r�¸��ƽ�����Դ늉������ƽ���ǵص��ƽ������ⲿ�·�o(w��)�����_�^(q��)�ָߵ��ƽ�����ߵ������^��ɿ��]�� A/D �ɼ��ķ�ʽ�O(sh��)Ӌ(j��)̎������(du��)�։���ʽ�еIJɘ��c(di��n)��Ҫ���]�։������x��ʹԓ�c(di��n)ͨ�^�ɘӶ˿ڵ������С�ڲɘ���Сݔ���������t�o(w��)���M(j��n)�вɘӡ�

��3���_�P(gu��n)��ݔ��������ԭ�t�DZ��Cݔ�����ƽ�ӽ��Դ늉������ƽ�ӽ����ƽ��I/O �ڵ����{���һ����ڷų��������(du��)С����Ԫ������������Dz��õ��ƽ���Ƶķ�ʽ��һ����r�£���ؓ(f��)�dҪ��С��10mA���t����оƬ���_ֱ�ӿ��ƣ������ 10~100mA �r(sh��)�������O�ܿ��ƣ��� 100mA��1A �r(sh��)�� IC ���ƣ����������t�m�����^������ƣ�ͬ�r(sh��)���hʹ�ù�늸��xоƬ��

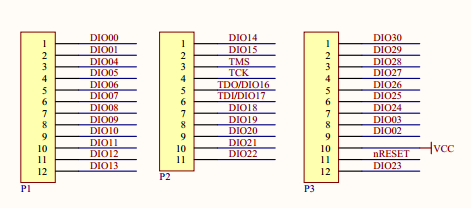

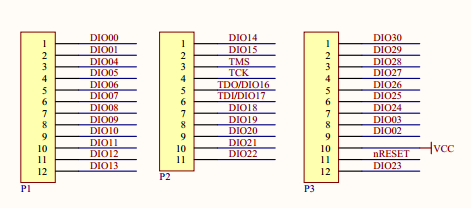

�@���҂����_�l(f��)��ĵ�I/O��ȫ��������(l��i)�������Ñ��M(j��n)�ж����_�l(f��)�͜y(c��)ԇ�(y��n)�C�����D��ʾ��

4. A/D�·�cD/A�·

��1��A/D�·��Ҫ���ǰ�˲ɘӻ���ԭ������(du��)����͡�����ͺ�늉��͂��������ò�ͬ�IJɼ��·������ɼ�����̖(h��o)����߀Ҫ���]����M(j��n)����̖(h��o)�Ŵ�

��2��D/A�·�����] MCU �����_ͨ�^�ηNݔ���·���ƌ�(sh��)�H��(du��)��

5.�����·

��(du��)������·Ҫע���O(sh��)Ӌ(j��)�������c���y(c��)��Ҫ�к��m����̖(h��o)���x��ʩ�ȡ����u(p��ng)���O(sh��)Ӌ(j��)�IJ���r(sh��)��һ��Ҫ�ژ�(g��u)����ݔ��ݔ���������z�y(c��)�ף��Է����Ų��e(cu��)�`�r(sh��)�y(c��)����

6.���]����

�����O(sh��)Ӌ(j��)�����H�H�Ǟ���ʡ늣�����ĺ�̎���ڽ������Դģ�K��ɢ��ϵ�y(t��ng)�ijɱ�����������ĜpСҲ�p����늴�ݗ��͟����ĸɔ_���S���O(sh��)��ضȵĽ��ͣ����������t����(y��ng)���L(zh��ng)��Ҫ��������һ����Ҫע�������c(di��n)��

��1�����������еĿ�����̖(h��o)��Ҫ���������������Ҳ�й��Ć��}��Ҫ���]�������������һ��(g��)�μ���ݔ����̖(h��o)�����Ҳ�͎�ʮ�����¡�����һ��(g��)���(q��)��(d��ng)�˵���̖(h��o)����������_(d��)������(j��)��������Ҫ���]��������茦(du��)ϵ�y(t��ng)�����ĵ�Ӱ푡�

��2�����õ�I/O�ڲ�Ҫ�ҿգ�����ҿյ�Ԓ��������һ�c(di��n)�c(di��n)�ɔ_�Ϳ��ܳɞ鷴��(f��)��ʎ��ݔ����̖(h��o)����MOS�����Ĺ��Ļ���ȡ�Q���T�·�ķ��D(zhu��n)�Δ�(sh��)��

��3����(du��)һЩ���СоƬ�Ĺ���Ҳ��Ҫ���]����(du��)�ڃ�(n��i)����̫��(f��)�s��оƬ�����Ǻ��y�_���ģ�����Ҫ�����_�ϵ�����_���������е�оƬ���_�ڛ]��ؓ(f��)�d�r(sh��)����늴�Ų���1��������ؓ(f��)�d�����Ժ��ܹ��ĺܴ�

7.���]�ͳɱ�

��1�����_�x�����ֵ�c���ֵ������һ��(g��)������裬����ʹ��4.5K-5.3K����裬���X�þ��x��(g��)����(sh��)5K����(sh��)���Ј�(ch��ng)�ϲ�����5K����ֵ����ӽ�����4.99K������1%���������5.1K������5%������ɱ��քe�Ⱦ��Ȟ�20%��4.7K��4����2����20%���ȵ������ֵֻ��1��1.5��2.2��3.3��4.7��6.8�ׂ�(g��)e����10������(sh��)��������Ƶأ�20%���ȵ����Ҳֻ�����ώNֵ������x��������ֵ�ͱ��ʹ�ø��ߵľ��ȣ��ɱ��ͷ��ˎױ����s������(l��i)�κκ�̎��

��2����Ҫʲô���x��õġ���һ��(g��)����ϵ�y(t��ng)�в�����ÿһ���ֶ������ڸ��٠�B(t��i)���������ٶ�ÿ���һ��(g��)�ȼ�(j��)���r(ji��)����Ҫ����������߀�o��̖(h��o)�����Ԇ��}����(l��i)�O���ؓ(f��)��Ӱ�.

����Ƕ��ʽ���̎�����Ҫ����Ƕ��ʽܛ���O(sh��)Ӌ(j��)��ҲҪ����Ӳ���O(sh��)Ӌ(j��)�������ܿ���Ӳ��ԭ��D���܉�����Ӳ���Ĺ���ԭ�����@���҂����ܸ��õľ�����Ч��Ƕ��ʽܛ�������{(di��o)ԇ�a(ch��n)Ʒ����Q�O(sh��)����ϕr(sh��)�����܉��ܛ��Ӳ���ĽǶȁ�(l��i)�������}�ͽ�Q���}�� ���Ͼ������@��Ҫ�ʹ�ҷ������P(gu��n)��Ƕ��ʽӲ���O(sh��)Ӌ(j��)��ע�����(xi��ng)��ϣ����(du��)ͬ�W(xu��)������������

Ƕ��ʽӲ���·�O(sh��)Ӌ(j��)

�r(sh��)�g��2018-03-22 ��(l��i)Դ��δ֪

Ƕ��ʽӲ���·�O(sh��)Ӌ(j��)

�r(sh��)�g��2018-03-22 ��(l��i)Դ��δ֪

11�¾͘I(y��)�L(f��ng)�ư�ح���н�Y18k����н11k�����¾͘I(y��)���c(di��n)

11�¾͘I(y��)�L(f��ng)�ư�ح���н�Y18k����н11k�����¾͘I(y��)���c(di��n) ʮ�¾͘I(y��)�L(f��ng)�ư�ح�x���A�� ��н�͘I(y��)�����ܶ����@

ʮ�¾͘I(y��)�L(f��ng)�ư�ح�x���A�� ��н�͘I(y��)�����ܶ����@ ���¾͘I(y��)�L(f��ng)�ư� | �͘I(y��)�΄�(sh��)���ԣ��A��W(xu��)�Ӆs���(sh��)����

���¾͘I(y��)�L(f��ng)�ư� | �͘I(y��)�΄�(sh��)���ԣ��A��W(xu��)�Ӆs���(sh��)���� ����T�ܿɐ� ���YҲ���� 8��н�Y���t

����T�ܿɐ� ���YҲ���� 8��н�Y���t ��һ�N���������e�˼ҵij���T����һ�N���YҲ�����e��

��һ�N���������e�˼ҵij���T����һ�N���YҲ�����e�� ���¾͘I(y��)�L(f��ng)�ư�|��һ�Q���@��(g��)��Ƹ��(bi��o)��(zh��n)���Ҷ��M(j��n)����(l��i)��

���¾͘I(y��)�L(f��ng)�ư�|��һ�Q���@��(g��)��Ƹ��(bi��o)��(zh��n)���Ҷ��M(j��n)����(l��i)�� �A���h(yu��n)Ҋ90+�(xi��ng)Ŀ�@����������2021���

f(xi��)ͬ�����(xi��ng)Ŀ��

�A���h(yu��n)Ҋ90+�(xi��ng)Ŀ�@����������2021���

f(xi��)ͬ�����(xi��ng)Ŀ�� �A���h(yu��n)Ҋ�s�@2021�vӍ��������ȿڱ�Ӱ����I(y��)����Ʒ

�A���h(yu��n)Ҋ�s�@2021�vӍ��������ȿڱ�Ӱ����I(y��)����Ʒ �A���h(yu��n)Ҋ��������2021����h���k��У��Ϣ�W(xu��)�ƺ���(li��n)��

�A���h(yu��n)Ҋ��������2021����h���k��У��Ϣ�W(xu��)�ƺ���(li��n)�� ��ůͬ�й���(chu��ng)�ѿ�(j��) 2019�A���h(yu��n)Ҋ�����������(hu��)���ع�

��ůͬ�й���(chu��ng)�ѿ�(j��) 2019�A���h(yu��n)Ҋ�����������(hu��)���ع� ������УAI�˹����܌W(xu��)�ƽ��O(sh��) �A���h(yu��n)Ҋ�˹������Y��

������УAI�˹����܌W(xu��)�ƽ��O(sh��) �A���h(yu��n)Ҋ�˹������Y�� �A���h(yu��n)Ҋ���������Ĵ�ʡ��(li��n)�W(w��ng)���(hu��)���s�@��(y��u)����I(y��)����

�A���h(yu��n)Ҋ���������Ĵ�ʡ��(li��n)�W(w��ng)���(hu��)���s�@��(y��u)����I(y��)����